FPGA数字信号处理(十七)多级CIC滤波器Verilog设计 |

您所在的位置:网站首页 › fpga cic滤波器 › FPGA数字信号处理(十七)多级CIC滤波器Verilog设计 |

FPGA数字信号处理(十七)多级CIC滤波器Verilog设计

|

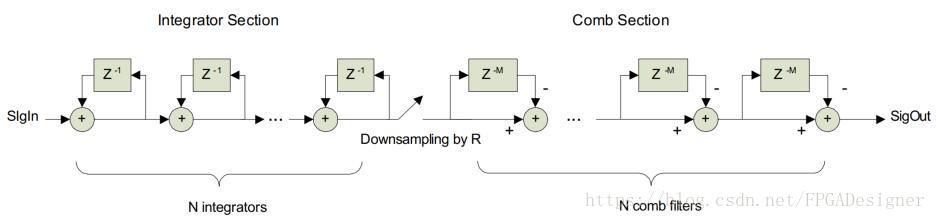

该篇是FPGA数字信号处理的第17篇,题接上篇,本文详细介绍多级CIC滤波器的特性、使用Verilog HDL设计多级CIC滤波器的方法。接下来两篇会介绍使用Quartus和Vivado的IP核设计CIC的方法。 多级CIC滤波器根据上一篇可知,单级CIC滤波器的第一旁瓣电平衰减固定为13.46dB,且与滤波器的阶数无关。这个值不满足通常的阻带衰减要求,解决方法就是通过级联CIC滤波器来达到更大的阻带衰减。事实上实际应用中采用的都是多级CIC滤波器。 ●频谱特性使用MATLAB的FDATOOL工具观察多级CIC滤波器的频谱。 点击最左边的小按钮,中间选择CIC滤波器,右边级数(Number Of Sections)设置为4,表示四级CIC滤波器。这里设置为对25MHz的Fs进行5倍抽取。可以看到第一旁瓣的衰减约为48dB,大概提升了4倍。 不过增加CIC滤波器的级数也有不利的影响:通带衰减也随着增加。换句话说,对于给定的通带衰减要求,多级CIC滤波器的通带范围会随着级数的增加而不断变窄。滤波器的设计不仅要考虑阻带误差容限,还要考虑通带误差容限,设计多级CIC滤波器时要注意考虑这个问题。 其实,CIC滤波器大多应用于抗混叠抽取/内插滤波器,也是因为上述的原因。因为在抗混叠应用中,有效信号频带往往远小于采样率,因此总可以设计出同时满足通带和阻带要求的CIC滤波器。 ●实现结构理论上多级CIC滤波器可以直接由多个单级CIC滤波器级联得到,但根据Noble恒等式(“先进行抽取或者插值,再进行线性滤波”与“先进行线性滤波,再进行抽取或者插值”这两者是可以等价的),可以将多级CIC滤波器结构变换为工程中实际应用的Hogenauer CIC滤波器结构。与直接将多个单级CIC滤波器级联相比,更加节省资源,也能提高计算速度。 抽取滤波器结构如下所示: 本设计在Vivado环境中完成并进行仿真。设计一个5阶的3级CIC滤波器,对输入数据进行5倍抽取。根据上文抽取滤波器的结构,使用Verilog HDL分别完成积分模块、抽取模块、梳状模块的设计。 ●积分模块由于积分运算会导致数据位宽扩展,首先需要确定积分器的输出数据位宽。可以借助如下公式,当输入信号为Bin位时,积分器最大可能输出位数为: |

【本文地址】

今日新闻 |

推荐新闻 |

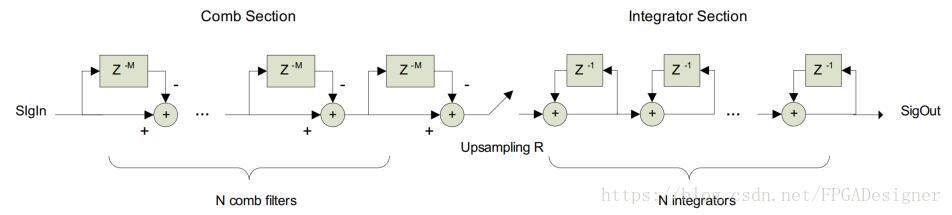

内插滤波器结构如下所示:

内插滤波器结构如下所示:

R为抽取/插值倍数,D为滤波器级数,N为滤波器阶数。本设计输入信号设置为10bit,则根据公式计算得到积分器输出数据为30Bits。设计的Verilog HDL代码如下:

R为抽取/插值倍数,D为滤波器级数,N为滤波器阶数。本设计输入信号设置为10bit,则根据公式计算得到积分器输出数据为30Bits。设计的Verilog HDL代码如下: